陆叶团队发明一种适用于超低功耗集成电路的超陡亚阈值摆幅(SS)晶体管器件

随着微电子技术进入后摩尔时代,兼备低功耗、高性能,并且与大规模硅基CMOS加工工艺相匹配的新型晶体管器件成为未来芯片技术的研究热点。作为一个理想开关,人们期待晶体管器件的亚阈值摆幅(SS)越小越好,而目前使用的硅基晶体管受到玻尔兹曼分布的限制,其室温SS极限为60 mV/dec,成为制约了先进芯片功耗进一步降低优化的关键瓶颈。

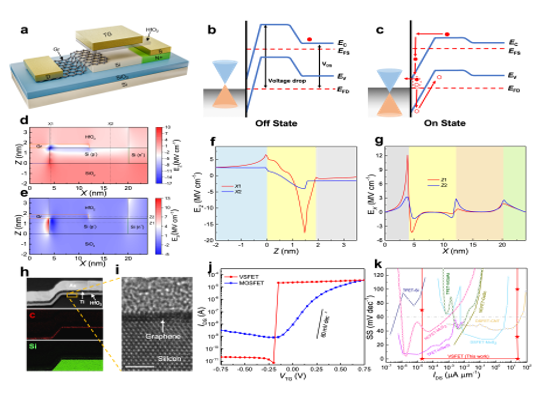

针对上述问题,复旦大学信息科学与工程学院陆叶研究员,联合万景研究员和微电子学院周鹏教授等,提出了一种基于石墨烯/硅异质结的硅基垂直亚阈值摆幅(nearly vertical SS)场效应晶体管(VSFET)。利用器件漏端异质结特殊能带结构,在低电压下即可产生超强电场并诱导碰撞离化,实现器件瞬间开启。实验结果表明,该器件在漏、源电压(VDS)低至0.4 V时,即可产生陡峭SS。值得一提的是,该器件实现了横跨6个电流数量级的16 µV/dec平均SS,远低于目前所有同类器件所能达到水平。并且由于碰撞离化区域远离栅氧化层栅极氧化层,并且VDS较小,使得器件的可靠性显著提高。

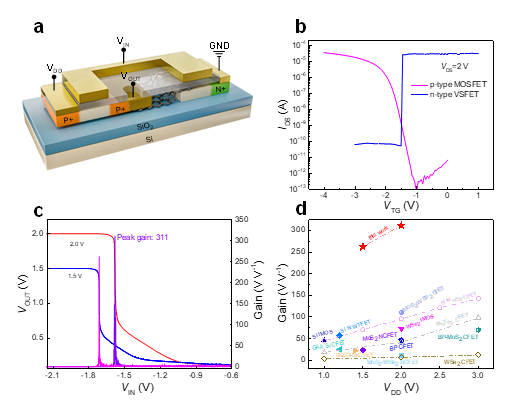

进一步为了证明VSFET器件在集成电路中使用的可行性,研究团队构建了一种基于VSFET器件的互补式逻辑反相器。该逻辑反相器在工作电压(VDD)等于2 V时,展现出了高达311的最大电压增益,高于目前其他同类器件所构建的反向器电路。这一结果表明了VSFET器件在构建高性能集成电路方面具有的巨大潜力。整体器件和电路架构基于硅基CMOS技术,也为未来大规模量产奠定了基础。

相关成果以“High drain field impact ionization transistors as ideal switches”为题发表在Nature Communications上。复旦大学博士研究生袁保卫为论文第一作者,陆叶研究员、万景研究员、周鹏教授为论文共同通讯作者。该工作获得了国家重点研发计划、国家自然科学基金、以及华为海思研究部的资助和支持。

版权所有©复旦大学智能电子与系统研究院版权所有

地址:淞沪路2005号复旦大学江湾校区交叉学科二号楼7楼 电话:021-31242626

loading......

loading......